nstructionsDownload and install Easycpu ENIAC package on a Windows platform. It can be installed on a Windows VM. https://sourceforge.net/projects/eniac/ Click , and point to the folder containt the

ENICA Design

Author: Dr. ssa Veronica Marchetti

Universita degli Studi di Roma “Tor Vergata”

Translated and Digested by: Dr. Sophia Scoggins

03/2019

- vCPU

- Architecture

The architecture of the vCPU is at 24bit. Are then used words in length 24bit equal to 16777216 without a sign, or between -83886608 and +83886608 with sign in two's-complement; all of the devices that will be briefly treated are conceived, designed, and implemented for work at 24bit.

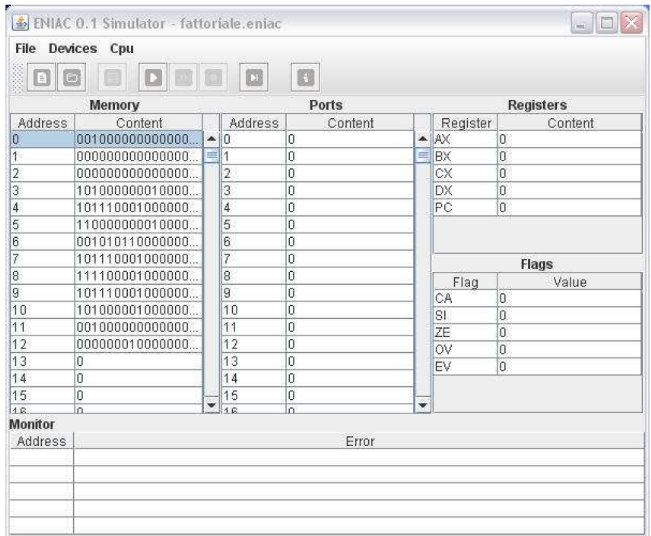

Figure 1. ENIAC Simulator Example fattoriable.eniac in Binary

- CPU A.L.U.

Arithmetic Logic Unit (ALU) is the real unit of calculation, The ALU is designed to perform operations between words to 24-bit with a sign, but

without a comma. It allows user to perform all the basic operations, including:

Sum;

Subtraction;

Increment;

Decrease;

Division;

Module;

Multiplication;

or Particular: since the product of the two numbers at 24bit makes one to

48bit, will be divided the result into two parts: R0 and R1;

Logical AND Logical;

Logical OR;

XOR Logic;

Logical NOT;

- Ports

Because of the architecture at 24bit, for simplicity, the cells of the doors can contain words of the same size. Are used to load I/O devices external. The doors are made from 212 cells. Through the port column, you can enable or disable devices to connect to the ports;

- Register

Basically there are five registers, suitable for different purposes:

AX: also called the accumulator is used as the default registry for most of the operations;

BX,CX,DX registers general purpose usable by the programmer;

PC: the Program Counter, i.e. the register that is in charge of saving the address of the memory cell that contains the next statement to be run.

- Flags

The flags are of registers of size 1, have the function to determine the flow of the program. For convenience, from now on, when we speak of registers, shall those of paragraph (1.5) while for register flags you will use the only the end flags. Can have the value 1 or 0, are divided into two categories and are set by the result of the last operation:

Simple;

Sign (SI): value is 1 if the result is negative, 0 otherwise;

Zero (ZE): value is 1 if the result is zero, 0 otherwise;

Equal (EV): value is 1 if the sum of the 1 bits of the result is even, 0 otherwise;

Complex; are specific to the operations of sum and multiplication:

Sum:

Carry-over (CA): it is 1 if there is a carry, 0 otherwise;

Overflow (OV): that is 1 if the MSB of the result differs from the MSB of the operands, 0 otherwise.

Product:

Carry-over (CA): value is 0 if the bits in R1 and the MSB in R0 are all equal, 1 otherwise;

Overaflow (OV): same as CA.

- CPU Instructions

- Operation Code (OpCode)

There are two classes of instructions: alpha and beta. Have tasks different because the alpha class allows you to manage operations beyond that the logic and storage; each statement can get to

have up to five different types of operands in the argument: (Indicating with “Operand” is the value).

Immediate: the operand is exactly the value to use;

example: ADD Z;

Direct address: the operand is in memory cell indicated.

Format: Memory -> Operand;

example: ADD @N;

Indirect address: operand is in memory cell whose address is in the memory cell indicated.

Format: Memory -> Memory -> Operand;

example: ADD @@N;

Register: the operand is in the register indicated.

Format: Log -> Operand;

example: ADD R;

Register Indirect: the operand is in memory cell whose address is in the indicated register.

Format: Register -> Memory -> Operand;

example: ADD @R;

For the operand, are devoted to the thirteen bit more to the right, and then you need to do clarifications on the meaning of Z,N,R:

Z: integer value between -4096 and +4095, since it is 213 two's-complement;

N: since the memory cells are 212 the address is between 0 and+4095;

R: the logs are five, will be therefore used five positive integers to the address referred to, for convenience, is shown the coding of the whole rather that in binary:

o AX: 0;

o BX: 1;

o CX: 6;

o DX: 7;

o PC: 4095;

Speaking of the beta-type, not subtypes, and contains primarily instructions for the control of the program flow, conditional jump, and unconditional. To avoid confusion, throughout the thesis we will refer to the “class alpha or class beta” with “alpha type or beta-type”.

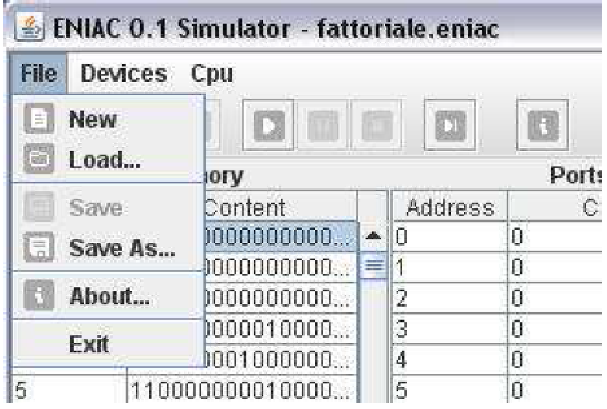

- Save File

The users can write code and save the files. Or load the file from the disk.

Figure 2. Save or Load Assembly Code

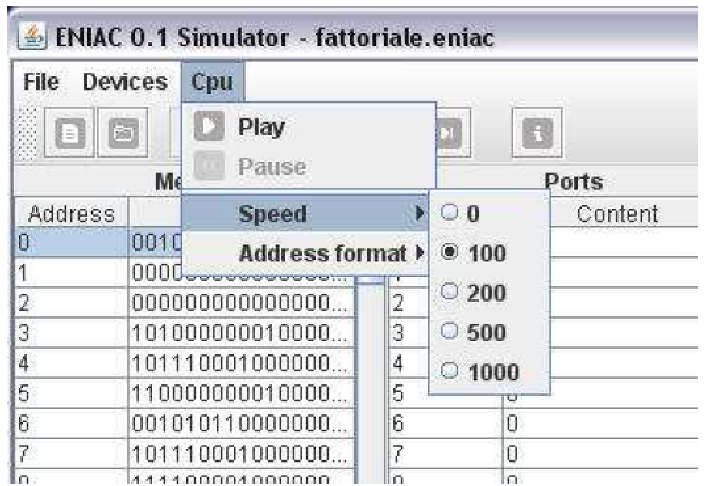

Menu Cpu: Click ‘Play’ to control the flow of execution as:

Step,

Play,

Pause,

Stop,

Speed: 0, 100, 200, 500, or 1000. The numbers express the pause time, in milliseconds (ms), between the execution of a statement and the next;

Figure 3. Execute the Assembly Code

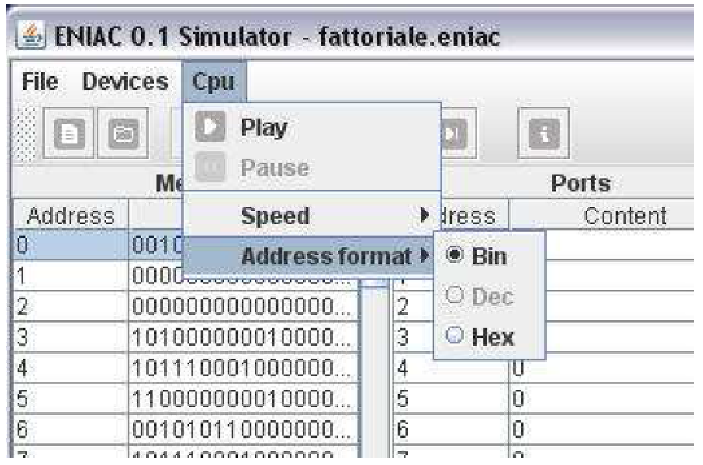

The Assembly code the ‘Content’ column can be in displayed in different address format:

Bin –- in binary #

Dec – in decimal #

Hex – in hexadecimal #

Syntax – in user friendly ASCII code

Figure 4. Assembly Code Display Format

Appendix A. Referenceshttp://sourceforge.net/projects/eniac/

“ENIAC”, rev, 26 Oct, 2007

“ENIAC”, rev, 6 Nov, 2007.

“ENIAC – design”

“ENIAC – specifica”